# Link for Analog Devices VisualDSP++® 1 User's Guide

#### How to Contact The MathWorks

www.mathworks.com

comp.soft-sys.matlab

www.mathworks.com/contact TS.html Technical Support

Web

Newsgroup

suggest@mathworks.com bugs@mathworks.com

doc@mathworks.com

service@mathworks.com info@mathworks.com

Product enhancement suggestions

Bug reports

Documentation error reports

Order status, license renewals, passcodes Sales, pricing, and general information

508-647-7000 (Phone)

508-647-7001 (Fax)

The MathWorks, Inc. 3 Apple Hill Drive Natick, MA 01760-2098

For contact information about worldwide offices, see the MathWorks Web site.

Link for Analog Devices VisualDSP++ User's Guide

© COPYRIGHT 2007 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use. modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### **Trademarks**

MATLAB, Simulink, Stateflow, Handle Graphics, Real-Time Workshop, SimBiology, SimHydraulics, SimEvents, and xPC TargetBox are registered trademarks and The MathWorks, the L-shaped membrane logo, Embedded MATLAB, and PolySpace are trademarks of The MathWorks, Inc.

Other product or brand names are trademarks or registered trademarks of their respective holders.

#### **Patents**

The MathWorks products are protected by one or more U.S. patents. Please see www.mathworks.com/patents for more information.

#### **Revision History**

May 2007 Online only New for Version 1.0 (Release 2007a+)

September 2007 Online only New for Version 1.1 (Release 2007b)

## **Contents**

| Getting Starte                                     |              |

|----------------------------------------------------|--------------|

|                                                    |              |

| What Is Link for VisualDSP++®?                     | 1-2          |

| The Structure and Components of Link for Analog    |              |

| Devices VisualDSP++®                               | 1-4          |

| Automation Interface                               | 1-4          |

| Project Generator                                  | 1-5          |

| Verification                                       | 1-5          |

| Automation Inter                                   | rface        |

| Getting Started with Automation Interface          | 2-2          |

| Introducing the Link for ADI VisualDSP++ Tutorial  | 2-2          |

| Running the Interactive Tutorial                   | 2-5          |

| Selecting Your Session and Processor               | 2-5          |

| Querying Objects for VisualDSP++                   | 2-6          |

| Loading Files into VisualDSP++                     | 2-8          |

| Running the Project                                | 2-10         |

| Closing the Connections or Cleaning Up VisualDSP++ | 2-11         |

| Constructing Objects                               | 2-13         |

| Example — Constructor for adivdsp Objects          | <b>2-1</b> 3 |

| Properties and Property Values                     | 2-15         |

| Setting and Retrieving Property Values             | 2-15         |

| Setting Property Values Directly at Construction   | 2-16         |

| Setting Property Values with set                   | 2-16         |

| Retrieving Properties with get                     | 2 - 17       |

Direct Property Referencing to Set and Get Values .....

Overloaded Functions for adivdsp Objects .....

2-17

2-18

| Project General                                                                                         |   |  |

|---------------------------------------------------------------------------------------------------------|---|--|

| Introducing Project Generator                                                                           |   |  |

| Using the Link for Analog Devices VisualDSP++                                                           |   |  |

| Blockset                                                                                                |   |  |

| Schedulers and Timing                                                                                   | 3 |  |

| Timer-Based Versus Asynchronous Interrupt Processing                                                    | 3 |  |

| Synchronous Scheduling                                                                                  | 3 |  |

| Asynchronous Scheduling                                                                                 | 3 |  |

| Scheduling Blocks                                                                                       | 3 |  |

| Asynchronous Scheduler Examples                                                                         | 3 |  |

| Uses for Asynchronous Scheduling                                                                        | 3 |  |

| Project Generator Tutorial                                                                              | 3 |  |

| Building the Model                                                                                      | 3 |  |

| Adding the Target Preferences Block to Your Model Specifying Simulink Configuration Parameters for Your | 3 |  |

| Model                                                                                                   | 3 |  |

| Setting Real-Time Workshop Options for Analog                                                           |   |  |

| Devices Processors                                                                                      | 3 |  |

| Setting Real-Time Workshop Category Options                                                             | 3 |  |

| Target Selection                                                                                        | 3 |  |

| Documentation                                                                                           | 3 |  |

| Build Process                                                                                           | 3 |  |

| Custom storage class                                                                                    | 3 |  |

| Debug Pane Options                                                                                      | 3 |  |

| Optimization Pane Options                                                                               | 3 |  |

| Link for Analog Devices VisualDSP++ Pane Options                                                        | 3 |  |

| Overrun Indicator and Software-Based Timer                                                              | 3 |  |

adivdsp Object Properties .....

Quick Reference to adivdsp Properties .....

2-19

2-19

|   | Options — Custom                                                                                      | 3-37<br>3-38                 |

|---|-------------------------------------------------------------------------------------------------------|------------------------------|

|   | Model Reference and Link for ADI VisualDSP++ How Model Reference Works                                | 3-42<br>3-42<br>3-43<br>3-45 |

| 1 | Verifica                                                                                              | tion                         |

|   | What is Verification?                                                                                 | 4-2                          |

|   | Using Processor-in-the-Loop  Processor-in-the-Loop Overview  PIL Block  Creating and Using PIL Blocks | 4-3<br>4-3<br>4-6<br>4-6     |

|   | Real-Time Execution Profiling Overview Profiling Program Execution                                    | 4-9<br>4-9<br>4-9            |

|   | Functions — By Cate                                                                                   | gory                         |

|   | Constructor                                                                                           | 5-2                          |

|   | File and Project Operations                                                                           | 5-3                          |

|   | IDDE Operations                                                                                       | 5-4                          |

|   | Processor Operations                                                                                  | 5-5                          |

|   | Debug Operations                            | 5-6        |

|---|---------------------------------------------|------------|

|   | Read/Write Operations                       | 5-7        |

|   | Get Information Operations                  | 5-8        |

|   | Object Information                          | 5-9        |

|   | Status Operations                           | 5-10       |

|   | Session Operations                          | 5-11       |

|   | Verification                                | 5-12       |

|   |                                             |            |

|   | Functions — Alphabetical                    | List       |

| , |                                             |            |

| • | Functions — Alphabetical  Blocks — By Categ |            |

| 7 |                                             | gory       |

| 7 | Blocks — By Categ                           | gory       |

| • | Blocks — By Categ                           | 7-2<br>7-3 |

8

| ^ | Examples                   | Examples |  |

|---|----------------------------|----------|--|

| ~ | Automation Interface A-2   | 2        |  |

|   | Working with Links A-2     | 2        |  |

|   | Asynchronous Scheduler A-5 | 2        |  |

|   | Project Generator A-5      | 2        |  |

|   | Verification A-2           | 2        |  |

|   | Index                      | K        |  |

# Getting Started

What Is Link for VisualDSP++®? (p. 1-2)

The Structure and Components of Link for Analog Devices VisualDSP++® (p. 1-4)

Introduces Link for Analog Devices VisualDSP++®

Describes the two components of Link for Analog Devices VisualDSP++®

#### What Is Link for VisualDSP++®?

Link for VisualDSP++ provides a connection between MATLAB® and the VisualDSP++ IDDE to enable users to access the processor, manipulate data on the processor, and manage projects within the IDDE, while simultaneously utilizing the MATLAB tools of numerical analysis and simulation. Using Link for Analog Devices VisualDSP++® you can perform the following tasks, and others related to Model-Based Design:

- Function calls Write scripts in MATLAB to execute any function in the VisualDSP++ IDDE

- Automation Write automated tests in MATLAB to be executed on your processor, including control and verification operations

- Host-Processor Communication Communicate with the processor directly from MATLAB, without going to the IDDE

- Verification and Validation

- Load and execute projects into the VisualDSP++ IDDE from the MATLAB command line

- Build and compile code, and then use vectors of test data and parameters to test the code

- Build and compile your code, and then download the code to the processor and execute it

- Design models Design models and algorithms in MATLAB and Simulink and run them on the processor

- Generate code— Generate executable code for your processor directly from the models designed in Simulink<sup>®</sup>, and execute it

Link for Analog Devices VisualDSP++® connects MATLAB® and Simulink® with VisualDSP++ integrated development and debugging environment from Analog Devices, Inc (ADI). Link for ADI VisualDSP++ enables you to use MATLAB and Simulink to debug and verify embedded code running on all Analog Devices DSPs that VisualDSP++ supports, such as the Blackfin, SHARC and TigerSHARC processor families.

Link for ADI VisualDSP++ includes a project generator component. With the project generator component, you can generate a complete project file for

VisualDSP++ from Simulink models, using C code generated with Real-Time Workshop®. Thus, you can use Real-Time Workshop and Real-Time Workshop Embedded Coder to generate generic ANSI C code projects for VisualDSP++ from Simulink models, that you can then build and run on Blackfin, SHARC, and TigerSHARC processors.

The following list suggests some of the uses for Link for ADI VisualDSP++:

- Create test benches in MATLAB and Simulink for testing your hand written or automatically generated code running on ADI DSPs

- Generate code and project files for VisualDSP++ from Simulink models using Real-Time Workshop and Real-Time Workshop Embedded Coder for rapid prototyping or deployment of a system or application

- Build, debug, and verify embedded code on ADI DSPs with MATLAB, Simulink, and VisualDSP++

- Perform processor-in-the-loop (PIL) testing of embedded code

# The Structure and Components of Link for Analog Devices VisualDSP++®

#### In this section...

"Automation Interface" on page 1-4

"Project Generator" on page 1-5

"Verification" on page 1-5

Link for Analog Devices VisualDSP++® comprises components—the Automation Interface component, the Project Generation component, and the Verification component. The Automation Interface component enables communication between MATLAB and Link for Analog Devices VisualDSP++®. It is built on MATLAB alone. The Project Generation component is built on SIMULINK and lets you build models, simulate them, and generate code from the models directly to the processor.

The Verification component offers capabilities that help you use Model-Based Design to validate and verify your projects. With the Verification component, you can simulate algorithms and processes in Simulink models and concurrently on your processor. Comparing the results helps verify the fidelity of you model or algorithm code.

#### **Automation Interface**

The Automation Interface component allows users to use MATLAB functions and methods to communicate with the VisualDSP++ IDDE to automate project management, to debug, to manipulate the data in the processor memory (internal and external) and registers, and to exercise functions from your project on the processor, and to communicate between the host and processor applications. The functionality provided by the automation interface component can be divided into the following categories:

- Debug Component Methods and functions for project automation, debugging, and data manipulation.

- Function Call Component Methods that allow the you to invoke individual functions on the processor.

• Host Processor Communication Component — Methods that support various standard communication protocols, such as BTC, TCP/IP, and UDP.

#### **Project Generator**

The Project Generator component is a collection of methods that utilize the VisualDSP++ API to create projects in VisualDSP++ and generate code with Real-Time Workshop<sup>®</sup>. With the interface, you can do the following:

- Automatic project-based build process Automatically create and build projects for code generated by Real-Time Workshop or Real-Time Workshop Embedded Coder.

- Custom code generation Use Link for ADI VisualDSP++ with any Real-Time Workshop System Target File (STF) to generate processor-specific and optimized code.

- Automatic downloading and debugging Debug generated code in the VisualDSP++ debugger, using either the instruction set simulator or real hardware.

- Create and build projects for VisualDSP++ from Simulink models Project Generator uses Real-Time Workshop or Real-Time Workshop Embedded Coder to build projects that work with Analog Devices processors.

- Generate custom code using the Configuration Parameters in your model with the system target files vdsplink ert.tlc and vdsplink grt.tlc.

## **Verification**

Verifying your processes and algorithms is an essential part of developing applications. The components of Link for ADI VisualDSP++ combine to provide the following verification tools for you to apply as you develop your code:

#### **Processor-in-the-Loop Cosimulation**

Use cosimulation techniques to verify generated code running in an instruction set simulator or real hardware environment.

#### **Execution Profiling**

Gather execution profiling measurements with VisualDSP++ instruction set simulator to establish the timing requirements of your algorithm.

## **Automation Interface**

Getting Started with Automation Interface (p. 2-2)

of creating and using objects and embedded objects

Guides you through the process

Constructing Objects (p. 2-13)

Explains what an adivdsp object is and how to construct one

Properties and Property Values (p. 2-15)

Describes how to work with objects, their properties and property values

adivdsp Object Properties (p. 2-19)

Describes the properties of link objects

## **Getting Started with Automation Interface**

#### In this section...

"Introducing the Link for ADI VisualDSP++ Tutorial" on page 2-2

"Running the Interactive Tutorial" on page 2-5

"Selecting Your Session and Processor" on page 2-5

"Querying Objects for VisualDSP++" on page 2-6

"Loading Files into VisualDSP++" on page 2-8

"Running the Project" on page 2-10

"Closing the Connections or Cleaning Up VisualDSP++" on page 2-11

Link for ADI VisualDSP++ provides a connection between MATLAB and a processor in VisualDSP++. You can use objects as a mechanism to control and manipulate a signal processing application using the computational power of MATLAB. This approach can help you while you debug and develop your application. Another possible use for automation is creating MATLAB scripts that verify and test algorithms that run in their final implementation on your production processor.

**Note** Before using the functions available with the objects, you must select a session in VisualDSP++. The object you create is specific to a designated session in VisualDSP++ IDDE.

#### Introducing the Link for ADI VisualDSP++ Tutorial

To get you started using objects for VisualDSP++ IDDE software, Link for ADI VisualDSP++ includes an example script vdsptutorial.m. As you work through this tutorial, you perform the following tasks that step you through creating and using objects for VisualDSP++ IDDE:

- 1 Select your session.

- **2** Create and query objects to VisualDSP++ IDDE.

- **3** Use MATLAB to load files into VisualDSP++ IDDE.

- **4** Work with your VisualDSP++ IDDE project from MATLAB.

- **5** Close the connections you opened to VisualDSP++ IDDE.

The tutorial covers some methods and functions for Link for ADI VisualDSP++. The functions listed first do not require an object. The functions listed after that require an existing adivdsp object before you can use the function syntax.

#### Functions for Working with VisualDSP++

The following table shows functions that do not require an object.

| Function     | Description                                                                                                                        |

|--------------|------------------------------------------------------------------------------------------------------------------------------------|

| listsessions | Return information about the boards that VisualDSP++ IDDE recognizes as installed on your PC.                                      |

| adivdsp      | Construct an object that refers to a VisualDSP++ IDDE session. When you construct the object you specify the session by processor. |

#### Methods for Working with adivdsp Objects in VisualDSP++

The following table presents some of the methods that require an adivdsp object.

| Methods | Description                                                                                                                                                                                                                 |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| add     | Add a file to a project                                                                                                                                                                                                     |  |

| address | Return the address and page for an entry in the symbol table in VisualDSP++ IDDE  Build the project in VisualDSP++  Change the working directory  Display the properties of an object that references a VisualDSP++ session |  |

| build   |                                                                                                                                                                                                                             |  |

| cd      |                                                                                                                                                                                                                             |  |

| display |                                                                                                                                                                                                                             |  |

| halt    | Terminate execution of a process running on the processor                                                                                                                                                                   |  |

| Methods                                     | Description                                                                                     |  |

|---------------------------------------------|-------------------------------------------------------------------------------------------------|--|

| info                                        | Return information about the object or session                                                  |  |

| isrunning                                   | Test whether the processor is executing a process                                               |  |

| load                                        | Load a built project to the processor                                                           |  |

| open                                        | Open a file in the project                                                                      |  |

| read                                        | Retrieve data from memory on the processor                                                      |  |

| reset                                       | Restore the program counter (PC) to the entry point for the current program                     |  |

| run                                         | Execute the program loaded on the processor                                                     |  |

| save                                        | Save files or projects                                                                          |  |

| visible                                     | Set whether VisualDSP++ IDDE window is visible on the desktop while VisualDSP++ IDDE is running |  |

| write Write data to memory on the processor |                                                                                                 |  |

#### Running VisualDSP++ on Your Desktop - Visibility

When you create an adivdsp object in the tutorial in the next section, Link for ADI VisualDSP++ starts VisualDSP++ in the background.

If VisualDSP++ is running in the background, it does not appear on your desktop, in your task bar, or on the **Applications** page in the Task Manager. It does appear as a process, idde.exe, on the **Processes** tab in Task Manager.

You can make the VisualDSP++ IDE visible with the function visible. The function isvisible returns the status of the IDE—is it visible on your desktop. To close the IDDE when it is not visible and MATLAB is not running, use the **Processes** tab in Windows Task Manager and look for idde.exe.

If an object that refers to VisualDSP++ exists when you close VisualDSP++, the application does not close. Windows moves it to the background (it becomes invisible). Only after you clear all objects that access VisualDSP++, or close MATLAB, does closing VisualDSP++ unload the application. You can see if VisualDSP++ is running in the background by checking in the Windows

Task Manager. When VisualDSP++ is running, the entry idde.exe appears in the **Image Name** list on the **Processes** tab.

#### **Running the Interactive Tutorial**

You have the option of running this tutorial from the MATLAB command line or entering the functions as described in the following tutorial sections.

To run the tutorial in MATLAB, click run vdspautointtutorial. This command launches the tutorial in an interactive mode where the tutorial program provides prompts and text descriptions to which you respond to move to the next section. The interactive tutorial covers the same information provided by the following tutorial sections. You can view the tutorial M-file used here by clicking vdspautointtutorial.m.

**Note** To run the interactive tutorial, you must have at least one session configured in VisualDSP++. If you do not yet have a session, use the Analog Devices VisualDSP++ Configurator to create a session to use for this tutorial.

## **Selecting Your Session and Processor**

Link for ADI VisualDSP++ IDDE requires that you have at least one session available for VisualDSP++. To help you select the session to use for this tutorial, and for any development work, Link for ADI VisualDSP++ provides a command line tool, called listsessions, which prints a list of the available sessions. So that you can use this function in a script, listsessions can return a MATLAB structure that you use when you want your script to select a session in the IDDE without your help.

**Note** The session you select is used throughout the tutorial.

1 To see a list of the sessions that you can use, enter the following command at the MATLAB prompt:

session list = listsessions

MATLAB returns a list that shows all the sessions that Link for ADI VisualDSP++ IDDE recognizes as available in your installation.

```

session_list =

'ADSP-21060 ADSP-2106x Simulator'

'ADSP-21362 ADSP-2136x Simulator'

```

**2** Use adjude to create an object that accesses a session in VisualDSP++.

```

vd = adivdsp('sessionname', 'ADSP-21362 ADSP-2136x Simulator', 'procnum', 0)

```

Sessionname and procnum are property names that specify the property to set. ADSP-21362 ADSP-2136x Simulator is the session to access, and 0 is the number of the processor to refer to in the session.

When you use adivdsp, you create an object, in this case vd, that refers to the session you specify in sessionname.

### **Querying Objects for VisualDSP++**

In this tutorial section you create the connection between MATLAB and VisualDSP++ IDDE. This connection, or object, is a MATLAB object, which for this session you save as variable vd. You use function adivdsp to create objects. When you create objects, adivdsp input arguments let you define other object properties, such as the global time-out. Refer to the adivdsp reference information for more about the input arguments.

Use the generated object vd to direct actions to your session processor. In the following tasks, vd appears in all function syntax that interact with IDDE session and the processor: The object vd identifies and refers to a specific session. You need to include the object in any method syntax you use to access and manipulate a project or files in a session in VisualDSP++.

1 Create an object that refers to your selected session and processor. Enter the following command at the prompt.

```

vd = adivdsp('sessionname', 'ADSP-21362 ADSP-2136x Simulator', 'procnum',0)

```

If you watch closely, and your machine is not too fast, you see VisualDSP++ appear briefly when you call adivdsp. If VisualDSP++ was not running

before you created the new object, VisualDSP++ launches and runs in the background.

Usually, you need to interact with VisualDSP++ while you develop your application. The function visible, controls the state of VisualDSP++ on your desktop. visible accepts Boolean inputs that make VisualDSP++ either visible on your desktop (input to visible  $\geq 1$ ) or invisible on your desktop (input to visible = 0). For this tutorial, you need to interact with the development environment, so use visible to set the IDDE visibility to 1.

**2** To make VisualDSP++ show on your desktop, enter the following command at the command prompt:

```

visible(vd,1)

```

3 Next, enter display(vd) at the prompt to see the status information.

```

ADIVDSP Object:

```

Session name : ADSP-21362 ADSP-2136x Simulator

Processor name : ADSP-21362 Processor type : ADSP-21362

Processor number: 0

Default timeout : 10.00 secs

Link for ADI VisualDSP++ provides three methods to read the status of a processor:

- info Return a structure of testable session conditions.

- display Print information about the session and processor.

- isrunning Return the state (running or halted) of the processor.

- **4** Type linkinfo = info(vd).

The vd link status information provides data about the hardware, as follows:

```

linkinfo =

```

procname: 'ADSP-21362'

proctype: 'ADSP-21362'

revision: ''

**5** Verify that the processor is running by entering

```

runstatus = isrunning(vd)

```

MATLAB responds, indicating that the processor is stopped, as follows:

```

runstatus =

```

0

#### Loading Files into VisualDSP++

You have established the connection to a processor and board. Using three methods you learned about the hardware, whether it was running, its type, and whether VisualDSP++ IDDE was visible. Next, give the processor something to do.

In this part of the tutorial, you load the executable code for the CPU in the IDDE. Link for ADI VisualDSP++ includes a tutorial project file for VisualDSP++. Through the next commands in the tutorial, you locate the tutorial project file and load it into VisualDSP++. The open method directs VisualDSP++ to load a project file or workspace file.

**Note** To continue the tutorial, you must identify or create a directory to which you have write access. Link for ADI VisualDSP++ cannot create a directory for you. If you do not have a writable directory, create one in Windows before you proceed with the rest of this tutorial.

VisualDSP++ has its own workspace and workspace files that are quite different from MATLAB workspace files and the MATLAB workspace. Remember to monitor both workspaces. The next steps change the working directory to your new writable directory.

1 Use cd to switch to the writable directory

```

prj_dir=cd('C:\vdsp_demo')

```

where the name and path to the writable directory is a string, such as C:\vdsp\_demo as used in the example. Replace C:\vdsp\_demo with the full path to your directory.

**2** Change your working directory to the new directory by entering the following command:

```

cd(vd,prj dir)

```

**3** Next, use the following command to create a new VisualDSP++ project named dot\_product\_c.dpj in the new directory:

```

new(vd,'dot product c.dpj')

```

Look in the IDDE to verify that your new project exists. Next you need to add source files to your project.

**4** Add the two provided source files, —dotprod.c and dotprod\_main.c to the project dot product c.dpj using the following two commands:

```

add(vd,'matlabroot\toolbox\vdsplink\vdspdemos\src\dotprod.c')

add(vd,'matlabroot\toolbox\vdsplink\vdspdemos\src\dotprod_main.c')

```

The variable matlabroot indicates the root directory of your MATLAB installation. Replace matlabroot with the path to MATLAB on your machine. For more information about the MATLAB root directory, refer to matlabroot in the MATLAB documentation.

**5** Open the files in the IDDE from MATLAB by issuing the following commands to open each file separately:

```

open(vd,'matlabroot\toolbox\vdsplink\vdspdemos\src\dotprod.c')

open(vd,'matlabroot\toolbox\vdsplink\vdspdemos\src\dotprod_main.c')

```

Switch to the IDDE to verify that the files are in your project and open.

**6** Save your project.

```

save(vd,'dot_product_c.dpj','project')

```

Your IDDE project is saved with the name dot\_product\_c.dpj in your writable directory. The input string 'project' specifies that you are saving a project file.

## **Running the Project**

After you create dot\_project\_c.dpj in the IDDE, you can use Link for ADI VisualDSP++ functions to create executable code from the project and load the code to the processor.

The next steps in this tutorial build the executable and download and run it on your processor.

1 Use the following build command to build an executable module from the project dot product c.dpj.

```

build(vd,30) % The optional input argument 30 sets the time out period to 30 seconds.

```

At the end of the build process, Link for ADI VisualDSP++ returns a value of 1 to indicate that the build succeeded. If the build process returns a 0, the build failed.

```

ans =

```

**2** To load the new executable to the processor, use load with the project file name and the object name. The name of the executable is dot\_product\_c.dxe, and it is stored with the project in your writable directory, in a subdirectory named debug.

```

load(vd, 'c:\vdsp demo\debug\dot product c.dxe',30);

```

Link for ADI VisualDSP++ provides methods to control processor execution—run, halt, and reset. To demonstrate these methods, use run to start the program you just loaded on to the processor, and then use halt to stop the processor.

**1** Try the following methods at the command prompt.

```

run(vd) % Start the program running on the processor.

halt(vd) % Halt the processor.

reset(vd) % Reset the program counter to start of program.

```

Use isrunning after the run method to verify that the processor is running. After you stop the processor, isrunning can verify that the processor has stopped.

## Closing the Connections or Cleaning Up VisualDSP++

Objects that you create in Link for ADI VisualDSP++ have connections to VisualDSP++. Until you delete these handles, the VisualDSP++ process (idde.exe in the Windows Task Manager) remains in memory. Closing MATLAB removes these objects automatically, but there may be times when it helps to delete the handles manually, without quitting MATLAB.

**Note** When you clear the last adivdsp object, Link for ADI VisualDSP++ closes VisualDSP++. When it closes the IDDE, it does not save current projects or files in the IDDE, and it does not prompt you to save them. A best practice is to save all of your projects and files before you clear adivdsp objects from your MATLAB workspace.

Use the following command to close the project files in VisualDSP++.

```

close(vd,'all','text')

```

Finally, to delete your link to VisualDSP++ use clear vd.

You have completed the Automation Interface tutorial using Link for Analog Devices VisualDSP++.

During the tutorial you performed the following tasks:

- 1 Selected your session.

- **2** Created and queried objects that refer to a session in Link for Analog Devices VisualDSP++ to get information about the session and processor.

- **3** Used MATLAB to load files into VisualDSP++, and used methods in MATLAB to run that file.

- **4** Closed the links you opened to VisualDSP++.

This set of tasks is used In any development work you do with signal processing applications. Thus, the tutorial provided here gives you a working process for using Link for ADI VisualDSP++ and your signal processing programs to develop programs for a range of Analog Devices processors.

## **Constructing Objects**

When you create a connection to a session in VisualDSP++ using the adivdsp function, you create an object. The object implementation relies on MATLAB object-oriented programming capabilities similar to the objects you find in MATLAB or Filter Design Toolbox.

The discussions in this section apply to the objects in Link for ADI VisualDSP++. Because adivdsp objects use the MATLAB programming techniques, the information about working with the objects, such as how you get or set properties, or use methods, apply to the objects you create in Link for ADI VisualDSP++.

Like other MATLAB structures, objects in Link for Analog Devices VisualDSP++ have predefined fields referred to as *object properties*.

You specify object property values by one of the following methods:

- Specifying the property values when you create the object

- Creating an object with default property values, and changing some or all of these property values later

For examples of setting link properties, refer to "Setting Property Values with set".

#### Example — Constructor for adivdsp Objects

The easiest way to create an object is to use the function adivdsp to create an object with the default properties. Create an object named vd referring to a session in VisualDSP++ by entering the following syntax:

```

vd = adivdsp

```

MATLAB responds with a list of the properties of the object vd you created along with the associated default property values.

#### ADIVDSP Object:

Session name : ADSP-21362 ADSP-2136x Simulator

Processor name : ADSP-21362 Processor type : ADSP-21362 Processor number: 0

Default timeout : 10.00 secs

The object properties are described in the adivdsp documentation.

**Note** These properties are set to default values when you construct links.

## **Properties and Property Values**

#### In this section...

"Setting and Retrieving Property Values" on page 2-15

"Setting Property Values Directly at Construction" on page 2-16

"Setting Property Values with set" on page 2-16

"Retrieving Properties with get" on page 2-17

"Direct Property Referencing to Set and Get Values" on page 2-17

"Overloaded Functions for adivdsp Objects" on page 2-18

Links (or objects) in this Link for ADI VisualDSP++ have properties associated with them. Each property is assigned a value. You can set the values of most properties, either when you create the link or by changing the property value later. However, some properties have read-only values. Also, a few property values, such as the board number and the processor to which the link attaches, become read-only after you create the object. You cannot change those after you create your link.

#### **Setting and Retrieving Property Values**

You can set Link for ADI VisualDSP++ for Analog Devices DSP link property values by either of the following methods:

- Directly when you create the link see "Setting Property Values Directly at Construction"

- By using the set function with an existing link see "Setting Property Values with set"

Retrieve Link for Analog Devices VisualDSP++ object property values with the get function.

Direct property referencing lets you either set or retrieve property values for adivdsp objects.

#### **Setting Property Values Directly at Construction**

To set property values directly when you construct an object, include the following entries in the input argument list for the constructor method adivdsp:

- A string for the property name to set followed by a comma. Enclose the string in single quotation marks as you do any string in MATLAB.

- The associated property value. Sometimes this value is also a string.

Include as many property names in the argument list for the object construction command as there are properties to set directly.

#### Example — Setting Link Property Values at Construction

Suppose that you want to create a link to a session in VisualDSP++ and set the following object properties:

- Link to the specified session.

- Connect to the first processor.

- Set the global time-out to 5 s. The default is 10 s.

Set these properties by entering

```

vd = adivdsp('sessionname','ADSP-21060 ADSP-2106x Simulator','procnum',0,'timeout',5);

```

The sessionname, procnum, and timeout properties are described in Link Properties, as are the other properties for links.

### **Setting Property Values with set**

After you construct an object, the set function lets you modify its property values.

Using the set function, you can change the value of any writable property of an object.

#### Example - Setting Link Property Values Using set

To set the time-out specification for the link vd from the previous section, enter the following syntax:

```

set(vd,'timeout',8);

get(vd,'timeout');

ans=

```

The display reflects the changes in the property values.

#### **Retrieving Properties with get**

You can use the get command to retrieve the value of an object property.

#### Example – Retrieving Link Property Values Using get

To retrieve the value of the sessionname property for vd2, and assign it to a variable, enter the following syntax:

```

session=get(vd2, 'sessionname')

session =

ADSP-21060 ADSP-2106x Simulator

```

#### **Direct Property Referencing to Set and Get Values**

You can directly set or get property values using MATLAB structure-like referencing. Do this by using a period to access an object property by name, as shown in the following example.

#### **Example - Direct Property Referencing in Links**

To reference an object property value directly, perform the following steps:

- 1 Create a link with default values.

- **2** Change its time-out and number of open channels.

```

vd = adivdsp;

vd.time = 6;

```

## **Overloaded Functions for adivdsp Objects**

Several methods and functions in Link for ADI VisualDSP++ have the same name as functions in other MathWorks products. These functions behave similarly to their original counterparts, but you apply them to an object. This concept of having functions with the same name operate on different types of objects (or on data) is called *overloading* of functions.

For example, the set command is overloaded for objects. After you specify your object by assigning values to its properties, you can apply the methods in this toolbox (such as address for reading an address in memory) directly to the variable name you assign to your object. You do not have to specify your object parameters again.

For a complete list of the methods that act on adivdsp objects, refer to the Chapter 6, "Functions — Alphabetical List" in the function reference pages.

## adivdsp Object Properties

#### In this section...

"Quick Reference to adivdsp Properties" on page 2-19

"Details About adivdsp Object Properties" on page 2-20

Link for ADI VisualDSP++ provides links to your processor hardware so you can communicate with processors for which you are developing systems and algorithms. Because Link for ADI VisualDSP++ uses objects to create the links, the parameters you set are called properties and you treat them as properties when you set them, retrieve them, or modify them.

This section details the properties for the objects for VisualDSP++. First the section provides tables of the properties, for quick reference. Following the tables, the section offers in-depth descriptions of each property, its name and use, and whether you can set and get the property value associated with the property. Descriptions include a few examples of the property in use.

MATLAB users may find much of this handling of objects familiar. Objects in Link for ADI VisualDSP++ behave like objects in MATLAB and the other object-oriented toolbox products. C++ programmers may already understand the concepts described in this section.

#### **Quick Reference to adivdsp Properties**

The following table lists the properties for the links in Link for ADI VisualDSP++. The second column indicates to which object the property belongs. Knowing which property belongs to each object in a link tells you how to access the property.

| Property<br>Name | User Settable?       | Description                                                                |

|------------------|----------------------|----------------------------------------------------------------------------|

| sessionname      | At construction only | Reports the name of the session in VisualDSP++ that the object references. |

| Property<br>Name | User Settable?       | Description                                                                                                                            |

|------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| procnum          | At construction only | Stores the number of the processor in the session. If you have more than one processor, this number identifies the specific processor. |

| timeout          | Yes/default          | Contains the global time-out setting for the link.                                                                                     |

Some properties are read only. Thus, you cannot set the property value. Other properties you can change at any time. If the entry in the User Settable column is "At construction only", you can set the property value only when you create the object. Thereafter it is read only.

#### **Details About adivdsp Object Properties**

To use the objects for VisualDSP++ interface, set values for the following:

- sessionname Specify the session with which the object interacts.

- procnum Specify the processor in the session. If the board has multiple processors, procnum identifies the processor to use.

- timeout Specify the global time-out value. (Optional. Default is 10 s.)

Details of the properties associated with adivdsp objects appear in the following sections, listed in alphabetical order by property name.

#### procnum

Property procnum identifies the processor referenced by an object for Link for Analog Devices VisualDSP++ IDDE. Use procnum to specify the processor you are working with in the session specified by sessionname. The VisualDSP++ Configurator assigns a number to each processor installed in each session. To determine the value of procnum for a processor, use listsessions or the Configurator.

To identify a processor, you need the sessionname and procnum values. For sessions with one processor, procnum equals 0. VisualDSP++ IDDE numbers the processors on multiprocessor boards sequentially from 0 to the total

number of processors. For example, on a board with four processors, the processors are numbered 0, 1, 2, and 3.

### sessionname

Property sessionname identifies the session referenced by a Link for Analog Devices VisualDSP++. When you create an object, you use sessionname to specify the session you are intending to interact with. To get the value for sessionname, use listsessions or the Analog Devices VisualDSP++ Configurator. The Configurator utility assigns the name for each session available on your system.

### timeout

Property timeout specifies how long VisualDSP++ waits for any process to finish. You set the global time-out when you create an object for a session in VisualDSP++. The default global time-out value 10 s. The following example shows the timeout value for object vd2.

```

display(vd2)

```

### ADIVDSP Object:

Session name : ADSP-21060 ADSP-2106x Simulator

Processor name : ADSP-21060 Processor type : ADSP-21060

Processor number: 0

Default timeout : 10.00 secs

# Project Generator

Introducing Project Generator (p. 3-2)

Using the Link for Analog Devices VisualDSP++ Blockset (p. 3-3)

Schedulers and Timing (p. 3-10)

Project Generator Tutorial (p. 3-17)

Setting Real-Time Workshop Options for Analog Devices Processors (p. 3-24)

Setting Real-Time Workshop Category Options (p. 3-26)

Model Reference and Link for ADI VisualDSP++ (p. 3-42)

Describes code generation with Project Generator

Describes the contents of the vdsplinklib blockset

Describes the timer-based and asynchronous schedulers

Takes you through the process of creating models in Simulink and generating code for your processors.

Provides the details on setting the Real-Time Workshop options when you generate code from your Simulink models to Analog Devices hardware.

Information about setting code generation options for models

Introduces model reference and how you use model reference with Link for Analog Devices VisualDSP++

# **Introducing Project Generator**

Project generator provides the following features for developing projects and generating code:

- Automated project building for VisualDSP++ that lets you create VisualDSP++ projects from code generated by Real-Time Workshop and Real-Time Workshop Embedded Coder. Project generator populates projects in the VisualDSP++ development environment.

- Blocks in the library vdsplinklib for controlling the scheduling and timing in generated code.

- Highly configurable code generation using model configuration parameters and target preferences block options.

- Capability to use Link for Analog Devices VisualDSP++ with one of two system target files to generate code specific to your processor.

- Highly configurable project build process.

- Automatic downloading and running of your generated projects on your processor.

To configure your Simulink models to use the Project Generator component, do one or both of the following tasks:

- Add a Target Preferences block from the Link for Analog Devices VisualDSP++ blockset (vdsplinklib) to the model.

- To use the asynchronous scheduler capability in Link for ADI VisualDSP++, add one or more hardware interrupt blocks or idle task block from the Link for Analog Devices VisualDSP++ blockset (vdsplinklib).

The following sections describe the blockset and the blocks in it, the scheduler, and the Project Generator component.

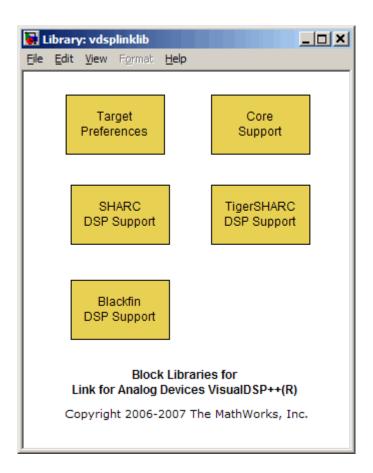

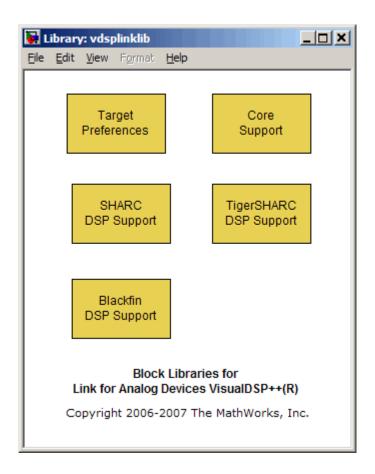

# Using the Link for Analog Devices VisualDSP++ Blockset

Link for Analog Devices VisualDSP++ block library vdsplinklib comprises block libraries that contain blocks designed for generating projects for specific processors. The following table describes these libraries.

| Library                                         | Description                                                           |

|-------------------------------------------------|-----------------------------------------------------------------------|

| Blackfin DSP Support (vdsplinklib_blackfin)     | Blocks for managing memory and task scheduling on Blackfin processors |

| Core Support (vdsplinklib_coresupport)          | Blocks for task scheduling and manipulating memory on ADI processors  |

| SHARC DSP Support (vdsplinklib_sharc)           | Blocks for task scheduling on SHARC processors                        |

| Target Preferences (vdsplinklib_tgtpref)        | Block that configures models for specific ADI processors              |

| TigerSHARC DSP Support (vdsplinklib_tigersharc) | Blocks for task scheduling on TigerSHARC processors                   |

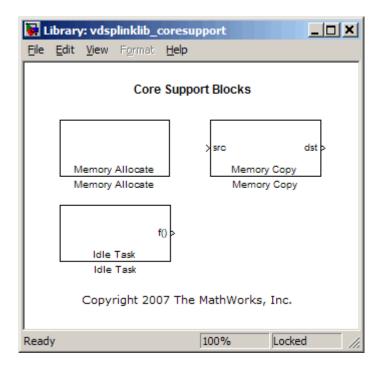

Blocks for the processor families are almost identical. Each block has a reference page that describes the options for the block. Use the Help browser to get more information about a block shown in any of the following figures.

The first figure shows the main library of libraries Link for Analog Devices VisualDSP++.

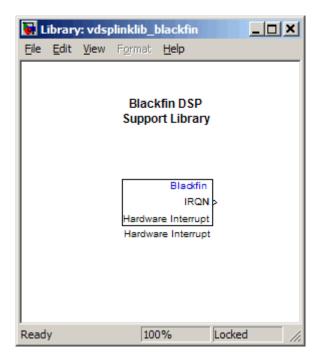

The next figure shows the Blackfin DSP Support library.

The SHARC DSP Support library contains the block in the next figure.

The target preferences library for all Analog Devices processors appears in the next figure.

The TigerSHARC DSP Support library appear in the next figure.

# **Schedulers and Timing**

### In this section...

"Timer-Based Versus Asynchronous Interrupt Processing" on page 3-10

"Synchronous Scheduling" on page 3-11

"Asynchronous Scheduling" on page 3-12

"Scheduling Blocks" on page 3-12

"Asynchronous Scheduler Examples" on page 3-12

"Uses for Asynchronous Scheduling" on page 3-15

The following sections describe how Link for Analog Devices VisualDSP++ provides timing and scheduling for generated code running on your processor.

# Timer-Based Versus Asynchronous Interrupt Processing

Code generated for periodic tasks, both single- and multitasking, runs out of the context of a timer interrupt. The generated code that represents model blocks for periodic tasks runs periodically, clocked by the periodic interrupt whose period is equal to the base sample time of the model.

**Note** In timer-based models, the timer counts through one full base-sample-time before it creates an interrupt. When the model is finally executed, it is for time 0.

This execution scheduling scheme is not flexible enough for some systems, such as control and communication systems that must respond to asynchronous events in real time. Such systems may need to handle a variety of hardware interrupts in an asynchronous, or aperiodic, fashion.

When you plan your project or algorithm, select your scheduling technique based on your application needs.

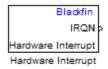

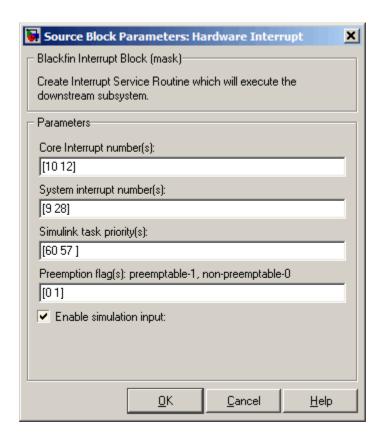

If your application processes hardware interrupts asynchronously, add the appropriate asynchronous scheduling blocks from the Link for Analog Devices VisualDSP++ library to your model, shown in the following table.

| Processor<br>Support<br>Library | Block Purpose                                        | Description                                                                                  |

|---------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Blackfin                        | Hardware Interrupt<br>for asynchronous<br>scheduling | Create interrupt service routine<br>to handle hardware interrupt on<br>Blackfin processors   |

| Core DSP                        | Idle Task                                            | Create task that runs as separate<br>thread for any Analog Devices<br>processor              |

| SHARC                           | Hardware Interrupt<br>for asynchronous<br>scheduling | Create interrupt service routine<br>to handle hardware interrupt on<br>SHARC processors      |

| Target<br>Preferences           | Target Preferences                                   | Configure model for Analog<br>Devices processor                                              |

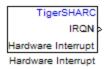

| TigerSHARC                      | Hardware Interrupt<br>for asynchronous<br>scheduling | Create interrupt service routine<br>to handle hardware interrupt on<br>TigerSHARC processors |

If your application does not service asynchronous interrupts, your model should include only the algorithm and device driver blocks that specify the periodic sample times. Generating code from a model like this automatically enables and manages a timer interrupt. The periodic timer interrupt clocks the entire model.

# **Synchronous Scheduling**

For code that runs synchronously in the context of the timer interrupt, each iteration of the model runs after an interrupt has been posted and serviced by an interrupt service routine (ISR). The code generated for Link for Analog Devices VisualDSP++ uses Timer 1. Timer 1 is configured so that the base rate sample time for the coded process corresponds to the interrupt rate. Link for Analog Devices VisualDSP++ calculates and configures the timer period to ensure the desired sample rate.

The minimum achievable base rate sample time depends on the algorithm complexity and the CPU clock speed. The maximum value depends on the maximum timer period value and the CPU clock speed.

If all the blocks in the model inherit their sample time value, and no sample time is defined explicitly, Simulink assigns a default sample time of 0.2 second.

# **Asynchronous Scheduling**

Link for Analog Devices VisualDSP++ facilitates modeling and automatically generating code for asynchronous systems by providing interrupt and task scheduling blocks as shown in the following table:

| Mode                                                | Block                       |

|-----------------------------------------------------|-----------------------------|

| Hardware Interrupt                                  | Blackfin, SHARC, TigerSHARC |

| Free-Running Task for Bare-Board<br>Code Generation | Idle Task                   |

# **Scheduling Blocks**

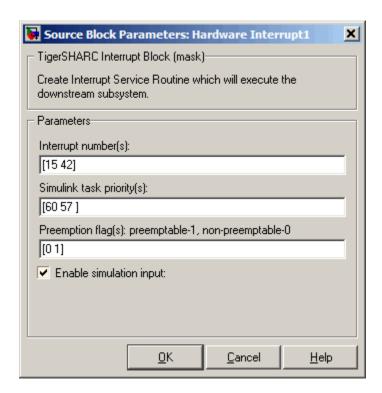

Link for Analog Devices VisualDSP++ Hardware Interrupt blocks enable selected hardware interrupts for the Analog Devices processors, generate corresponding ISRs, and connect them to the corresponding interrupt service vector table entries.

When you connect the output of the Hardware Interrupt block to the control input of a function-call subsystem, the generated subsystem code is called from the ISRs each time the interrupt is raised.

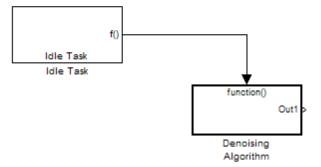

The Idle Task block specifies one or more functions to execute as background tasks in the code generated for the model. The functions are created from the function-call subsystems to which the Idle Task block is connected.

## Asynchronous Scheduler Examples

After you identify the blocks to use, you can use an asynchronous (real-time) scheduler for your application. With the asynchronous scheduler you can

define interrupts and tasks to occur when you want them to by using blocks from the following libraries:

- Blackfin DSP Support

- SHARC DSP Support

- TigerSHARC DSP Support

Also, you can schedule multiple tasks for asynchronous execution using the blocks.

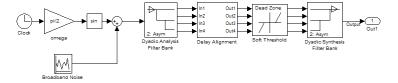

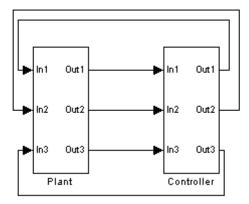

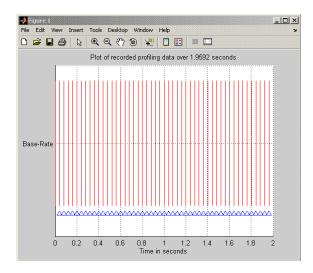

The following figures show a model updated to use the asynchronous scheduler rather than the synchronous scheduler.

**Note** You cannot run the example models. They provide example configurations only. They will not run or build without additional blocks.

### **Before**

## **After**

## Model Inside the Function Call Subsystem Block

# **Uses for Asynchronous Scheduling**

The following sections present common cases for the scheduling blocks described in the previous sections.

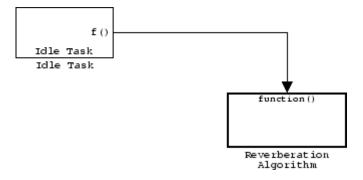

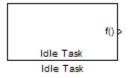

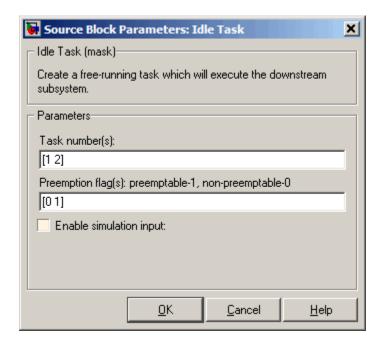

### **Idle Task**

The following model illustrates a case where the reverberation algorithm runs in the context of a background task in bare-board code generation mode.

The function generated for this task normally runs in free-running mode—repetitively and indefinitely. However, the input and output blocks in this subsystem run in blocking mode. As a result, subsystem execution of the reverberation function is the same as the subsystem described for the

Free-Running Task. Task execution is data driven via a background DMA interrupt-controlled ISR, shown in the following figure.

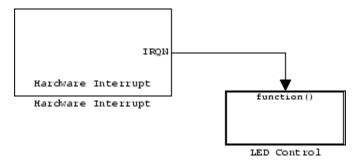

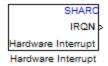

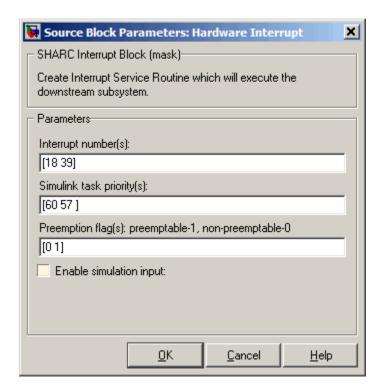

### Hardware Interrupt Triggered Task

In the next figure, you see a case where a function (control an LED) runs in the context of a hardware interrupt triggered task.

In this model, the Hardware Interrupt block installs a task that runs when it detects an external interrupt. This task then performs the specified operation.

# **Project Generator Tutorial**

### In this section...

"Building the Model" on page 3-18

"Adding the Target Preferences Block to Your Model" on page 3-18

"Specifying Simulink Configuration Parameters for Your Model" on page 3-21

In this tutorial you build a model and generate a project from the model into VisualDSP++.

**Note** The model demonstrates project generation only. You cannot build and run the model on your processor without additional blocks.

To generate a project from a model, complete the following tasks:

- 1 Use Simulink blocks, Signal Processing Blockset blocks, and blocks from other blocksets to create the model application.

- **2** Add the target preferences block from the Link for Analog Devices VisualDSP++ Target Preferences library to your model. Verify and set the block parameters for your hardware. In most cases, the default settings work fine.

- **3** Set the configuration parameters for your model, including the following parameters:

- Solver parameters such as simulation start and solver options

- Real-Time Workshop options such as processor configuration and processor compiler selection

- **4** Generate your project.

- **5** Review your project in VisualDSP++.

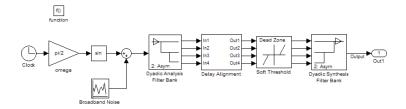

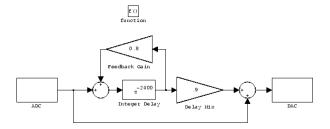

# **Building the Model**

To build the model for audio reverberation, follow these steps:

- 1 Start Simulink.

- 2 Create a new model by selecting File > New > Model from the Simulink menu bar.

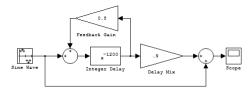

- **3** Use Simulink blocks and Signal Processing Blockset blocks to create the following model.

Look for the Integer Delay block in the Discrete library of Simulink and the Gain block in the Commonly Used Blocks library. Do not add the Custom Board block at this time.

4 Save your model with a suitable name before continuing.

# Adding the Target Preferences Block to Your Model

So that you can configure your model to work with Analog Devices processors, Link for Analog Devices VisualDSP++ includes a block library containing a target preferences block for Analog Devices processor, Target Preferences.

Entering vdsplinklib\_tgtpref at the MATLAB prompt opens this window showing the library blocks. This block library is included in Link for Analog Devices VisualDSP++ vdsplinklib blockset in the Simulink Library browser.

To add the Target Preferences block to your model, follow these steps:

- 1 Double-click Link for Analog Devices VisualDSP++ in the Simulink Library browser to open the vdsplinklib blockset.

- **2** Click the library Target Preferences to see the blocks available for your processor.

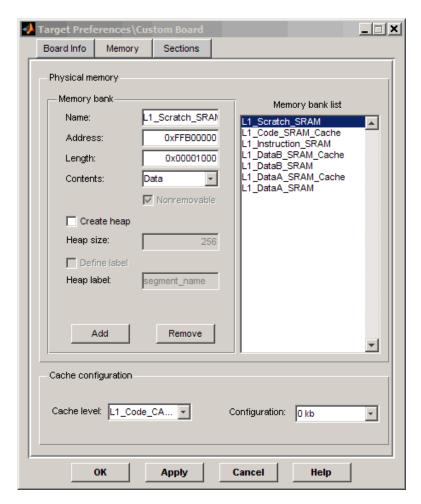

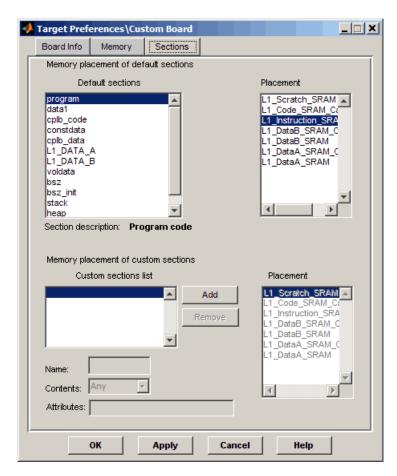

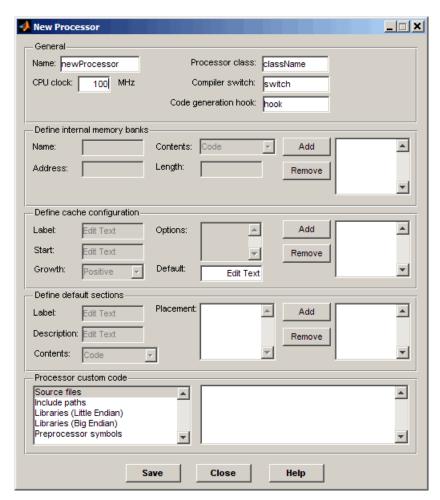

- **3** Drag and drop the Custom Board block to your model as shown in the following figure.

- **4** Double-click the Custom Board block to open the block dialog box.

- **5** In the Block dialog box, select your processor from the **Processor** list.

- 6 Verify the CPU clock value.

- **7** Select the session name from the **Session name** list. Verify that the session processor matches the one you selected from the **Processor** list.

- **8** Review the settings on the **Memory** and **Sections** tabs to verify that they are correct for the processor you selected.

- $\boldsymbol{9}$  Click  $\boldsymbol{OK}$  to close the Target Preferences dialog box.

You have completed the model. Next, configure the model configuration parameters to generate a project in VisualDSP++ from your model.

# Specifying Simulink Configuration Parameters for Your Model

The following sections describe how to configure the build and run parameters for your model. Generating a project, or building and running a model on the processor, starts with configuring model options in the Configuration Parameters dialog box in Simulink.

## **Setting Solver Options**

After you have designed and implemented your digital signal processing model in Simulink, complete the following steps to set the configuration parameters for the model:

- 1 Open the Configuration Parameters dialog box and set the appropriate options on the Solver category for your model and for Link for Analog Devices VisualDSP++.

- Set **Start time** to 0.0 and **Stop time** to inf (model runs without stopping). If you set a stop time, your generated code does not honor the setting. Set this to inf for completeness.

- Under Solver options, select the fixed-step and discrete settings from the lists.

- Set the **Fixed step size** to Auto and the **Tasking Mode** to Single Tasking.

**Note** Generated code does not honor Simulink stop time from the simulation. Stop time is interpreted as inf. To implement a stop in generated code, you must put a Stop Simulation block in your model.

Ignore the Data Import/Export, Diagnostics, and Optimization categories in the Configuration Parameters dialog box. The default settings are correct for your new model.

### **Setting Real-Time Workshop Options**

To configure Real-Time Workshop to use the correct processor files and to compile and run your model executable file, you set the options in the Real-Time Workshop category of the **Select** tree in the Configuration Parameters dialog box. Follow these steps to set the Real-Time Workshop options to generate code tailored for your DSP:

- 1 Select Real-Time Workshop on the **Select** tree.

- 2 In Target selection, click **Browse** to select the system target file for Analog Devices—vdsplink\_grt.tlc. It may already be the selected target file.

- Clicking **Browse** opens the **System Target File Browser** to allow you to changes the system target file.

- **3** On the **System Target File Browser**, select the system target file vdsplink\_grt.tlc, and click **OK** to close the browser.

Real-Time Workshop updates the **Template makefile** and **Make command** values with the appropriate files based on your system target file selection.

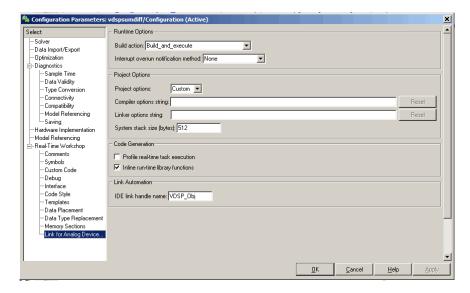

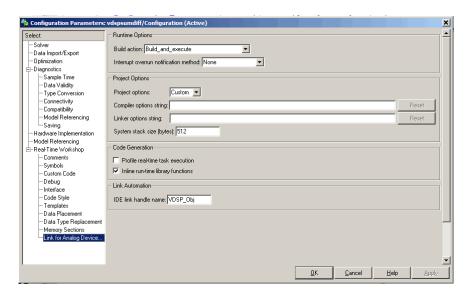

## **Setting Link for ADI VisualDSP++ Options**

After you set the Real-Time Workshop options for code generation, set the options that apply to your Analog Devices processor.

- 1 From the **Select** tree, choose Link for Analog Devices VisualDSP++ to specify code generation options that apply to the processor.

- **2** Under **Code Generation**, select the **Inline run-time library functions** option. Clear all other options.

- 3 (optional) Under Link Automation, provide a name for the handle in IDE handle name.

- **4** Set the following options in the dialog box under **Project options**:

- Set **Project options** to Custom.

- Set Compiler options string and Linker options string to blank.

- **5** Change the category on the **Select** tree to Hardware Implementation.

- **6** Verify that the Device type is the correct value for your processor—ADI Blackfin, ADI SHARC, or ADI TigerSHARC.

- 7 Change the category back to Link for Analog Devices VisualDSP++.

- **8** Set the following **Runtime** options:

- Build action: Create\_project.

- Interrupt overrun notification method: Print message.

You have configured the Real-Time Workshop options that let you generate a project for your processor. A few Real-Time Workshop categories on the **Select** tree, such as Comments, Symbols, and Optimization do not require configuration for use with Link for ADI VisualDSP++. In some cases, you may decide to set options in the other categories.

For your new model, the default values for the options in these categories are correct. For other models you develop, you may want to set the options in these categories to provide information during the build and to run TLC debugging when you generate code. Refer to your Simulink<sup>TM</sup> and Real-Time Workshop<sup>TM</sup> documentation for more information about setting the configuration parameters.

## **Creating Your Project**

After you set the configuration parameters and configure Real-Time Workshop to create the files you need, you direct Real-Time Workshop to create your project:

- 1 Click **OK** to close the Configuration Parameters dialog box.

- 2 Click Incremental Build ( ) on the model toolbar to generate your project into VisualDSP++.

When you press with Create\_project selected for **Build action**, the automatic build process starts VisualDSP++ and populates a new project in the development environment.

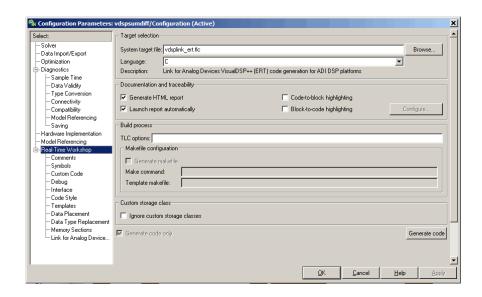

# Setting Real-Time Workshop Options for Analog Devices Processors

Before you generate code with the Real-Time Workshop, set the fixed-step solver step size and specify an appropriate fixed-step solver if the model contains any continuous-time states. At this time, you should also select an appropriate sample rate for your system. Refer to the *Real-Time Workshop*® *User's Guide* for additional information.

**Note** Link for ADI VisualDSP++ does not support continuous states in Simulink models for code generation. In the **Solver options** in the Configuration Parameters dialog box, you must select discrete (no continuous states) as the **Type**, along with Fixed step.

To open the Configuration Parameters dialog box for your model, select **Simulation > Configuration Parameters** from the menu bar.

The following figure shows the Real-Time Workshop **Select** tree categories when you are using Link for Analog Devices VisualDSP++.

In the **Select** tree, the categories provide access to the options you use to control how Real-Time Workshop builds and runs your model. The first categories under Real-Time Workshop in the tree apply to all Real-Time Workshop targets including the processor and always appear on the list.

The last category under Real-Time Workshop is specific to Link for Analog Devices VisualDSP++ system target files vdsplink\_grt.tlc and vdsplink ert.tlc and appears when you select either target file.

When you select your target file in Target Selection on the **Real-Time Workshop** pane, the options change in the tree.

For Link for Analog Devices VisualDSP++, the target file to select is vdsplink\_grt.tlc. Selecting either the vdsplink\_grt.tlc or vdsplink\_ert.tlc adds options specific to Link for Analog Devices VisualDSP++ to the **Select** tree. The vdsplink\_grt.tlc file is appropriate for all projects. Select vdsplink\_ert.tlc when you are developing projects or code for embedded processors (requires Real-Time Workshop Embedded Coder) or you plan to use Processor-in-the-Loop features.

The following sections present each Real-Time Workshop category and the options available in each.

# **Setting Real-Time Workshop Category Options**

### In this section...

"Target Selection" on page 3-27

"Documentation" on page 3-27

"Build Process" on page 3-28

"Custom storage class" on page 3-29

"Debug Pane Options" on page 3-29

"Optimization Pane Options" on page 3-30

"Link for Analog Devices VisualDSP++ Pane Options" on page 3-31

"Overrun Indicator and Software-Based Timer" on page 3-36

"Link for Analog Devices VisualDSP++ Default Project Options — Custom" on page 3-37

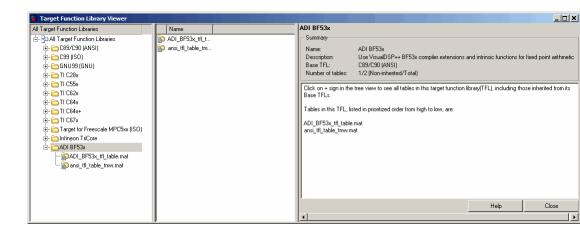

"Target Function Library and Link for ADI VisualDSP++" on page 3-38

Use the options in the **Select** tree under **Real-Time Workshop** to perform the following configuration tasks.

- Determine your processor, either Link for ADI VisualDSP++ or some other processor if you are not using Link for Analog Devices VisualDSP++.

- Specify your documentation needs.

- Configure your build process.

- Specify whether to use custom storage classes.

When you select one of the Link for Analog Devices VisualDSP++ system target files, the Link for Analog Devices VisualDSP++ category appears in the **Select** tree as shown in the following figure.

## **Target Selection**

## System target file

Clicking **Browse** opens the Target File Browser where you select vdsplink\_grt.tlc as your Real-Time Workshop **System target file** for Link for Analog Devices VisualDSP++. When you select your target configuration, Real-Time Workshop chooses the appropriate system target file, template make file, and make command. You can also enter the target configuration filename, and Real-Time Workshop fills in the **Template makefile** and **Make command** selections.

If you are using Real-Time Workshop Embedded Coder software, select the vdsplink\_ert.tlc target file in **System target file**.

## **Documentation**

Two options control HTML report generation during code generation.

### **Generate HTML report**

After you generate code, this option tells the software whether to generate an HTML report that documents the C code generated from your model. When you select this option, Real-Time Workshop writes the code generation report files in the html subdirectory of the build directory. The top-level HTML report file is named <code>modelname\_codegen\_rpt.html</code> or <code>subsystemname\_codegen\_rpt.html</code>. For more information about the report, refer to the online help for Real-Time Workshop. You can also use the following command at the MATLAB prompt to get more information.

docsearch 'Generate HTML report'

### Launch report automatically

This option direct Real-Time Workshop to open a MATLAB Web browser window and display the code generation report. When you clear this option, you can open the code generation report (modelname\_codegen\_rpt.html or subsystemname\_codegen\_rpt.html) manually in a MATLAB Web browser window or in another Web browser manually.

## **Build Process**

### Template makefile

Real-Time Workshop uses template makefiles to generate the makefile for building the executable file. During the automatic build process, MATLAB issues the make\_rtw command. make\_rtw extracts information from the template makefile vdsplink\_grt.tmf and creates the actual makefile vdsplink.mk. When Real-Time Workshop compiles the model, it uses the actual makefile to select the compiler to use to generate the compiled code.

### Make command

When you generate code from your digital signal processing application, select **Generate makefile** and use the standard command make\_rtw as the **Make command**. In the **Build process** area in the Real-Time Workshop category, enter make\_rtw for the **Make command**. Parameters you set in this dialog box belong to the model you are building. They are saved with the model and stored in the model file.

## **Custom storage class**

When you generate code from a model employing custom storage classes (CSC), clear **Ignore custom storage classes**. This setting is the default value for Link for Analog Devices VisualDSP++ and for Real-Time Workshop Embedded Coder.

When you select **Ignore custom storage classes**, storage class attributes and signals are affected in the following ways:

- Objects with CSCs are treated as if you set their storage class attribute to Auto.

- The storage class of signals that have CSCs does not appear on the signal line, even when you select Storage class from Format > Port/Signals Display in your Simulink menus.

**Ignore custom storage classes** lets you switch to a processor that does not support CSCs, such as the generic real-time target (GRT), without reconfiguring your parameter and signal objects.

### Generate code only

The **Generate code only** option does not apply to targeting with Link for Analog Devices VisualDSP++. To generate source code without building and executing the code on your processor, select Link for Analog Devices VisualDSP++ from the **Select** tree. Then, under **Runtime**, select Create\_project for **Build action**.

## **Debug Pane Options**

Real-Time Workshop uses the Target Language Compiler (TLC) to generate C code from the <code>model.rtw</code> file. The TLC debugger helps you identify programming errors in your TLC code. Using the debugger, you can perform the following actions:

- View the TLC call stack.

- Execute TLC code line-by-line.

- Analyze or change variables in a specified block scope.

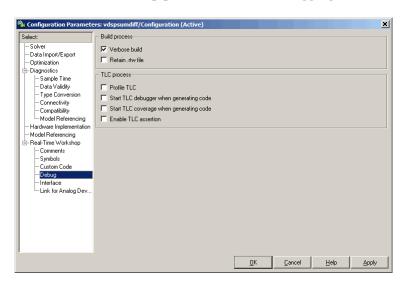

When you select Debug from the **Select** tree, you see the Debug options as shown in the next figure. In this dialog box, you set options that are specific to Real-Time Workshop process and TLC debugging.

For details about using the options in Debug, refer to "About the TLC Debugger" in your Real-Time Workshop Target Language Compiler documentation.

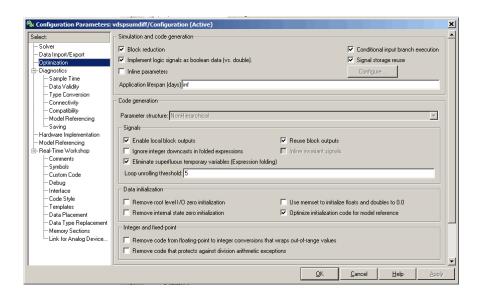

# **Optimization Pane Options**

On the Optimization pane in the Configuration Parameters dialog box, you set options for the code that Real-Time Workshop generates during the build process. Use these options to tailor the generated code to your needs. Select Optimization from the **Select** tree on the Configuration Parameters dialog box. The figure shows the Optimization pane when you select the system target file vdsplink\_grt.tlc under **Real-Time Workshop system target file**.